Griffin

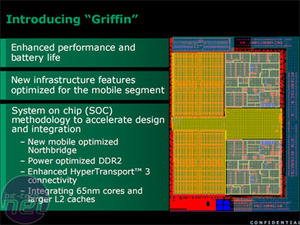

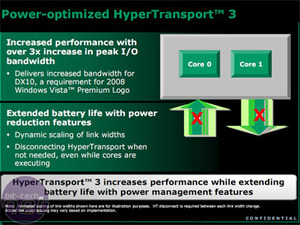

Griffin is AMD's dedicated future mobile CPU which will have initially dual core (with the possibility of quad core later), be built on 65nm process and integrate a larger exclusive 1MB L2 cache per core. There will still be the internal crossbar switch to provide an internal communication mechanism between cores, HyperTransport and memory controller. In addition the CPU will also have a completely new northbridge optimised for power saving, and run on DDR2-667, 800 and possibly 1066 DDR2 SODIMMs.It will also use the updated HyperTransport 3.0 for faster interaction between itself and the system resources, however it has the option to dynamically clock itself down asynchronously (5x to 1x) in either direction, or turn itself off completely to save power. The only problem being the HyperTransport system needs to completely momentarily disconnect itself between link width changes.

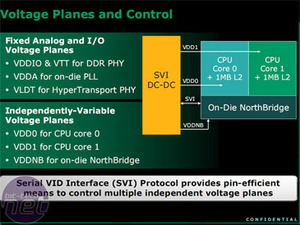

Whereas AM2+ introduces split plane voltages for allowing two independent power planes, Griffin has three: one for each CPU and another for the northbridge. This, in combination with the course and fine logic gating technique introduced in the Phenom allows huge power saving potential, only powering exactly what is needed.

The new northbridge contains an improved DRAM prefetcher for improved DRAM efficiency, and the separate power plane means it now uses less voltage, and thus power than the CPU cores. When used with a local frame buffer on the integrated graphics chipset, the northbridge can potentially be turned off completely if the system is only displaying a single image, like a Powerpoint presentation.

Power Efficiency done a dozen times better

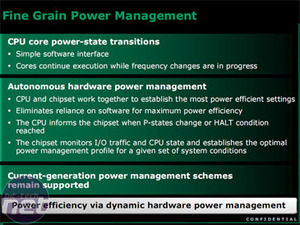

Not only does each core operate on a different voltage plane but it also can run at independent frequencies. Now the hardware supports core clocks that dynamically scale in 1/8th fraction frequencies and three corresponding voltage drops depending on system load. In addition to this, there is a lower C1 Halt state where the CPU clock switches off completely, and also global C3 deep sleep and C4 hibernate states.The cores can continue thread executions while changing frequencies and voltages, and further fruits of the AMD-ATI integration can be seen here, as the CPU works together with the chipset to provide the most efficient power saving situation. The chipset reads the CPU I/O rate, and the CPU also informs the chipset when P-state changes or HALT sleep/hibernate conditions are enabled so the chipset can establish an optimal power management profile for the rest of the system.

The system is designed to eliminate the need for software to change system states; however the CPU still requires OS optimisation. Windows Vista allows state changes on the microsecond response rate, rather than millisecond like in Windows XP. Combine that with a future DirectX 10 integrated graphics chipset and naturally AMD recommends using Vista.

These power state improvements are now coordinated with multiple on-die thermal sensors that can affect system state changes and reduce the P-state of either the memory controller or CPUs with a simple command, reducing the addition to the heat output, keeping the system stable and maintaining the life of the silicon. If the temperature keeps rising beyond even the lowest operating and lower voltage frequencies then the system will be sent to sleep.

MSI MPG Velox 100R Chassis Review

October 14 2021 | 15:04

Want to comment? Please log in.